Developing integrated circuits or chips containing thousands or even millions of transistors on a single chip is called the Very Large Scale Integration, or VLSI design flow. The continuous VLSI design flow comprises many steps, such as specification, entry, verification, synthesis, layout, and manufacture. Let’s get an in-depth understanding of the VLSI Design Flow in this blog.

- Design Specification

The first step in the VLSI design flow is to develop design specifications containing functional requirements, performance goals, and other limitations. In this stage, the chip designer and customer discuss the chip’s application, power consumption, performance targets, and area constraints.

- Design Entry

After the design requirements have been established, a design entry or description must be written. This phase involves establishing a high-level representation of the design with the aid of hardware description languages like Verilog or VHDL. In the design entry phase, you’ll set the design’s functional blocks, linkages, and behaviour specifications.

- Design Verification

As a crucial part of the VLSI design flow, verification ensures that any problems with the design have been resolved before moving on. The design is checked against the requirements by using testing, simulation, and formal verification.

- Synthesis

After the design is checked for accuracy, the next phase is to conduct the synthesis. Through the use of synthesis tools, the high-level design description is translated into a gate-level representation. The design is optimized for performance, power consumption, and footprint during synthesis. The synthesis process results in a gate-level netlist that describes the architecture using logic elements like gates and flip-flops.

- Layout

The chip’s layout is the next step after synthesis. What you see on the chip is the layout, which is the physical representation of the design. The process entails physically arranging the gates, flip-flops, and other components on the chip’s surface and then connecting them with wiring. Factors like chip size, power distribution, signal integrity, and manufacturing limits must be carefully considered during the layout design.

- Design Rule Check, DRC

After the blueprint is complete, a Design Rule Check is performed on the design. The DRC procedure compares the design to the fabricator’s manufacturing regulations and guidelines. You can rest assured that your design will be free of flaws during manufacture using DRC.

- Physical Verification

After the DRC, the layout goes through physical verification, including checks for layout-dependent impacts like cross-talk, electrostatic discharge protection, and other manufacturing-related concerns. The purpose of physical verification is to check if the design can be manufactured and if there are any faults in the physical implementation.

- Tape-out

After the design has been physically verified and the layout verified as being manufacturable, it is ready for tape-out. Tape-out refers to generating the final design data in a format that can be delivered to a fabrication plant for chip manufacture. Details about the chip’s layout, mask layers, and fabrication processes are all recorded on the tape-out data.

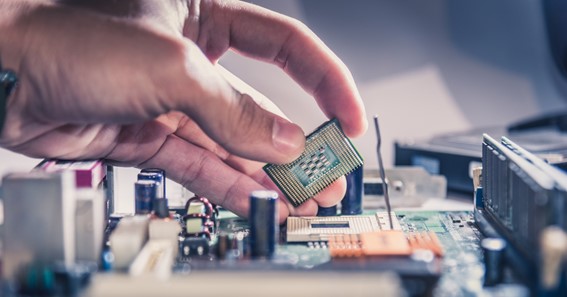

- Fabrication

When the chip has been taped out, it is sent to a fab, which is short for “fabrication facility” for semiconductors. The fab uses the tape-out data to fabricate the chip on a silicon wafer using a variety of steps such as deposition, lithography, etching, and doping.

Conclusion

Semiconductor engineers and designers must understand the VLSI design process to create complicated integrated circuits that meet modern electronic device requirements. It advances microelectronics by designing and fabricating advanced semiconductors for cellphones, computers, automotive, and aerospace systems.